What Intel is doing, in fact, is "binning" its chips, just like it does its processors.

In all likelihood, the 875P silicon will come from the same wafers and essentially be the same chips as Intel's upcoming Springdale chipset, but Springdale will be a cheaper, higher-volume product. (Springdale chipsets will differ from the 875P only in that they won't include PAT or support for ECC memory types.)

The 875P will cost a little more, and will be aimed at workstation users and enthusiasts.

Intel probably plans to pick the very fastest Canterwood/Springdale MCH (north bridge) chips and test them to verify they're capable of running with PAT enabled.

The best of those chips will be sold as 875P MCH chips.

With PAT enabled, the 875P memory controller will perform some internal memory handling tasks faster, yielding a one-clock improvement in the time for a CPU request to perform memory access and another one-clock improvement in the DRAM chip select process.

The total improvement is two clocks for each chip select (CS) process. CS happens at the beginning of a typical memory access, so cutting the CS process by two cycles could lead to real-world reductions in memory access latency.

Intel emphasizes that 875P chipsets are tested rigorously, at full operating speed, for their ability to run with PAT enabled, so Canterwood motherboards ought to be plenty stable under normal operating conditions. Intel is also quick to point out that PAT happens internally in the memory controller, while external memory interfaces run according to their specifications.

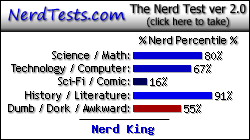

A block diagram of the 875P chipset — Source: Intel

LibreOffice

LibreOffice Firefox

Firefox

No comments:

Post a Comment